什么是电源管理芯片的低功耗设计

低功耗设计是一系列技术和方法的集合,只在降低集成电路芯片的整体动态和静态功耗。

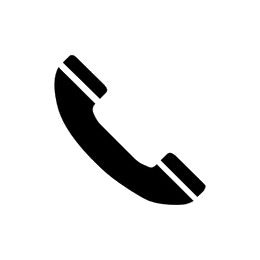

如图1所示的功率的各个分量,低功耗设计的目标是尽可能减少单个分量的功率,从而降低整体功耗。功率方程包含动态和静态功率的分量。动态电源由开关电源和短路电源组成;而静态功率由泄漏或在没有活动时流经晶体管的电流组成。每个电源组件的值与以下任一因素相关:

活动

频率

过渡时间

容性负载

电压

漏电流

峰值电流

例如,电压越高,每个组件消耗的功率越高,导致总功率越高。相反,电压越低,总功率越低。为了以最低的功耗实现最佳性能,我们通过各种低功耗技术和方法对每个不同因素进行了权衡和测试。

对低功耗设计的需求

正在推动新特性和功能的界限,所有这些都包含在便携式,手持式和电池供电的设备上。对于此类产品,通过最小化功耗来延长电池寿命是一个巨大的差异化因素,并且对其最终用户的应用极其重要。缩短设备从关闭/睡眠状态变为开/活动状态所需的时间同样重要,因为最终用户希望获得无缝体验和更长的电池寿命。

对于"插件"产品,功耗也很重要,因为它可以通过需要散热器和复杂的冷却系统,增加电力成本等来影响系统的整体成本。例如,在使用大规模并行系统的服务器场中,单个芯片的功耗降低可以显著节省功耗,因为它在整个系统中使用。通过使用更新、更节能的IC升级这些系统来节省功耗和成本,可以显著提高能耗。

低功耗设计技术

有许多低功耗设计技术可用,其中一些使用起来非常简单,而另一些则更复杂。

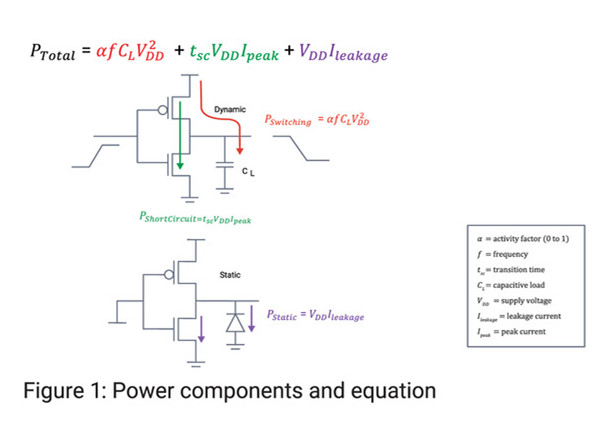

时钟门控

这种技术通常在逻辑合成期间执行,其中使能漏极被优化为时钟门控结构,从而节省多路复用器面积并降低时钟网络的整体开关活动(参见图2)。关于功率方程,目标是降低容性负载(通过面积减小)和活动系数,从而降低动态功率的开关功率分量。这是一种非常简单且随时可用的技术,可以减少功率和面积。但是,它确实依赖于逻辑合成工具来执行此优化。幸运的是,这种技术是众所周知的,并且在大多数工具和流中都得到了很好的支持。

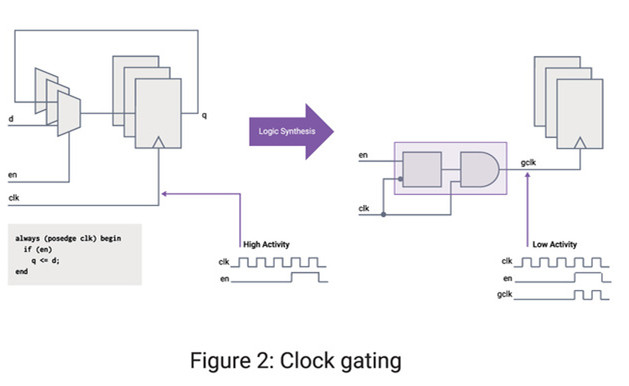

多电压

这是一种技术,其中芯片的功能通过性能特征进行分区 - 也许一个块是高性能的,而芯片的其余部分是较低的性能,如图3所示。为了实现高性能模块的目标,通常需要更高的电压;同时为了节省较低性能模块的功率,可以使用较低的电压。这代替了在较高电压下设计整个模块,后者更简单但功率更大。在功率方程中,电压降低,从而降低每个静态和动态功率分量。对于多电压设计,在单独的电压孤岛中进行设计存在复杂性,其中岛之间的电压交叉可能需要"电平移位器"(LS)单元,并且需要实现和分析不同电压特性下的模块。

电源门控

这是一种技术,其中IC上的功能也被分区,就像多电压一样,但这次电源域的电源连接到电源开关,如图4所示。电源门控有效地完全关闭了一个块的电源。在功率方程中,这会将电压归零并关闭电源,从而节省模块关闭时间的静态和动态时间。电源门控通常提供最积极的节能效果,因此,在保持功能的同时,尽可能频繁地关闭尽可能多的域是一个理想的目标。为了通过电源门控实现这种节能效果,必须在设计中实现电源开关,这需要隔离门在关闭时将电源域的边界钳位到已知值。必须考虑设计的电源状态以及给定电压的开/关状态组合。最后,必须实现控制电源开关和隔离使能信号的电源管理单元(PMU)。在断电和上电期间,这些信号的顺序必须正确,这样关断期间的值才能在正确的时间箝位到正确的值。

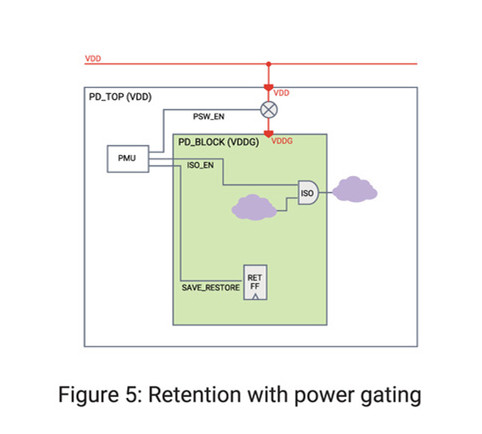

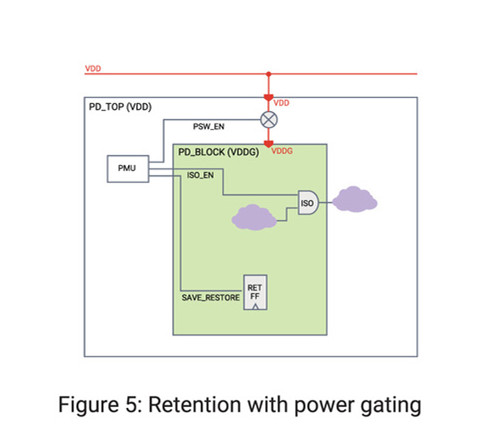

通过电源门控保持

保留(或寄存器保留)是一种与电源门控一起使用的技术。在每个关机块中,当该块为 OFF 时,该块中的一个子集或该块中的所有翻牌都保存了其以前的值。当块打开电源时,将恢复以前保存的值。请务必在块断电时保存块的状态,以便块可以快速恢复其以前的状态,而不必从 INIT 状态循环到当前状态。这通过减少获取保存状态所需的时间和步骤来节省功耗,并缩短了整体爬坡时间以恢复块的先前功能。除了电源门控所需的一切之外,库中还必须存在可以映射到 RTL 中所需寄存器的保留触发器。除了用于电源门控的信号外,还需要将保存/恢复信号与控制这些信号的顺序一起添加到PMU中(参见图5)。

先进技术

低功耗设计有许多更先进的技术,包括前面提到的技术的组合。使用较低电压和电源门控的模块,并具有隔离、保持和电平转换器,这在许多现代芯片中很常见。良好的偏置、零引脚保持漏极、专用的低功耗库单元、动态电压和频率调节(DVFS)、自适应电压和频率调节(AVFS)以及定制设计只是业界使用的其他一些先进低功耗技术。

低功耗设计方法

假设已指定系统的示例,已执行系统仿真,已完成微体系结构,已对技术节点,IP等进行了低功耗选择,并完成了RTL和UPF的编码。鉴于此,低功耗设计和验证方法有五个主要阶段可用于设计IC。

静态功耗验证和探索

在静态验证中,第一步是确保设计流程(RTL、UPF 和 SDC)的输入在结构和语法上都是正确的。根据定义,静态验证不使用测试向量,因此这是在进入仿真或实现流程之前检查输入的一种非常有效的方法。Lint和CDC检查通常对于确保您的RTL干净很重要。UPF检查可以独立完成,也可以使用相应的RTL进行,以确保它们是干净的,SDC也可以与RTL一起静态检查。在功耗探索中,可以使用估计的开关或仿真中的实际波形来驱动对RTL功耗的早期估计。可以尽早做出选择,通过执行早期的RTL功耗分析来改进设计的整体架构。

动态功率验证和分析

在动态功率验证中,有几个重要方面需要检查。首先,PMU控制信号的顺序是否正常工作,以关断、箝位隔离、保存、恢复、移除隔离钳位和上电。这是一个非常重要的检查,将设计RTL和UPF放在一起,以确保设计正常运行。接下来,在设计中看到什么类型的波形和切换活动?这将决定使用的动态功率,因为它取决于活动因子。活性因子越高,使用的功率就越大。因此,产生的波形对于在过程的早期和后期准确估计功率非常重要。

软件驱动的功耗分析

对于基于仿真的低功耗流,能够捕获设计功率曲线的正确峰值窗口非常重要。仿真允许查看更广泛的数据集,使人们能够选择

最有价值的窗口,以生成波形以估计功率。

电源实现

基于RTL的预测功率估计、逻辑综合、DFT插入和物理实现都扮演着重要的低功耗特定角色。基于 RTL 的预测功率估计允许在很早的时候,通过早期的功率估计进行 RTL 修改。在逻辑综合中,RTL、SDC和UPF现在经过静态和动态验证,被映射到技术门。特定于电源的隔离、电平转换器和保持单元也映射到栅极,其中时序、面积和功率都是生成网表和相关UPF的成本函数的一部分。DFT 插入也会发生,通常在此期间同时发生。一旦网表和UPF完成,另一轮检查将在此级别静态和动态地完成 - 一旦干净,结果将被输入到物理实现中。在物理实现中,平面布置是在考虑宏观布局和电源布线的情况下完成的。然后进行放置,其中电源开关被物理插入和放置;并执行放置、路由估计、逻辑优化和时钟树综合的迭代,以再次权衡时序、面积和功耗。最后,进行布线步骤,完成优先信号(时钟、电源使能、交换机连接)的预布线,然后详细布线其余部分的设计 - 所有这些都强调更精细地降低功耗,同时仍然试图满足时序和区域目标。

低功耗设计工具

该方法的每个阶段所需的低功耗设计工具包括:

1.静态功耗验证和探索。静态验证需要用于Lint 和 CDC 的工具,以确保 RTL 是干净的。对于 UPF,需要 UPF 检查器来确保 UPF 是干净的。对于功耗探索,需要 RTL 功耗估算工具。

2.动态功耗验证和分析。功耗感知模拟器对于验证电源时序和生成波形是必要的。功耗感知调试工具以及可以利用RTL仿真数据并转换为门级仿真数据的工具也是必要的,因为这对于节省时间和为功耗分析提供非常准确的波形至关重要。

3.软件驱动的功耗分析。通过仿真,可以产生基于周期的功率,观察更长的行为,并且可以选择正确的功率/定时窗口进行功率分析。

4.电源实现。实现低功耗设计需要基于RTL的预测功率估计、逻辑合成、DFT插入(扫描插入、MBIST、逻辑BIST等)和物理实现(楼层规划、放置、时钟树综合、布线)。

5.签核。UPF 检查网表和 UPF 以及 PGNetlist 和 UPF"对于确保电源意图正确且在整个流程中保持至关重要。具有功耗感知功能的逻辑等效性检查对于确保在整个流程中保留逻辑功能也至关重要。静态时序分析和功耗分析工具对于验证时序和提供准确的功耗估算结果至关重要。

侵权必删

Please let us know if there is any infringement